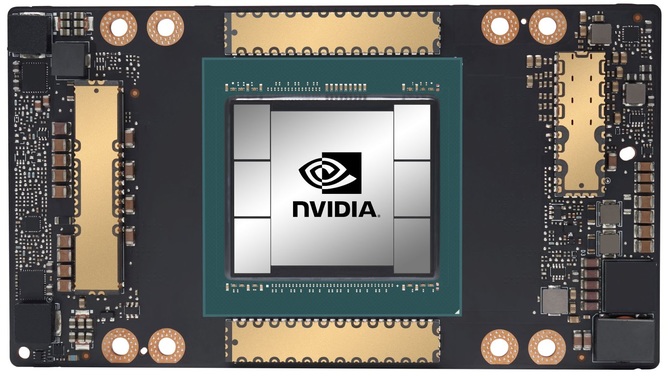

Niedawno Raja Koduri, inżynier Intela twierdził, że krzem „Ponte Vecchio” Xe HP był „wielkim tatusiem” procesorów graficznych Xe i „największym układem opracowanym w Indiach”, większym niż 35-miliardowy tranzystor Xilinix VU19P FPGA. Jednak okazało się, że NVIDIA chce ustanowić nowy rekord. Krzem „Ampere” A100 ma aż 54 miliardy tranzystorów wtłoczonych w pojedynczą matrycę 7 nm, oczywiście nie licząc tych z pamięci HBM2E.

NVIDIA Ampere A100 – wydajność

Według firmy NVIDIA, nowy układ to 20-krotny wzrost wydajności w porównaniu do swojego poprzednika opartego na Volcie. Układ oferuje także 2,5-krotny wzrost wydajności FP64 w porównaniu do „Volta”. NVIDIA wynalazła również nowy format liczb dla obliczeń AI, o nazwie TF32 (tensor float 32). TF32 wykorzystuje 10-bitową mantysę FP16 i 8-bitowy wykładnik FP32, co daje nowy, wydajny format. NVIDIA przypisuje temu 20-krotny wzrost wydajności w porównaniu do „Volty”. Rdzeń tensora trzeciej generacji wprowadzony z Ampere obsługuje natywnie FP64. Innym kluczowym celem projektu NVIDIA jest wykorzystanie zjawiska „rzadkości” w sieciach neuronowych, aby zmniejszyć ich rozmiar i poprawić wydajność.

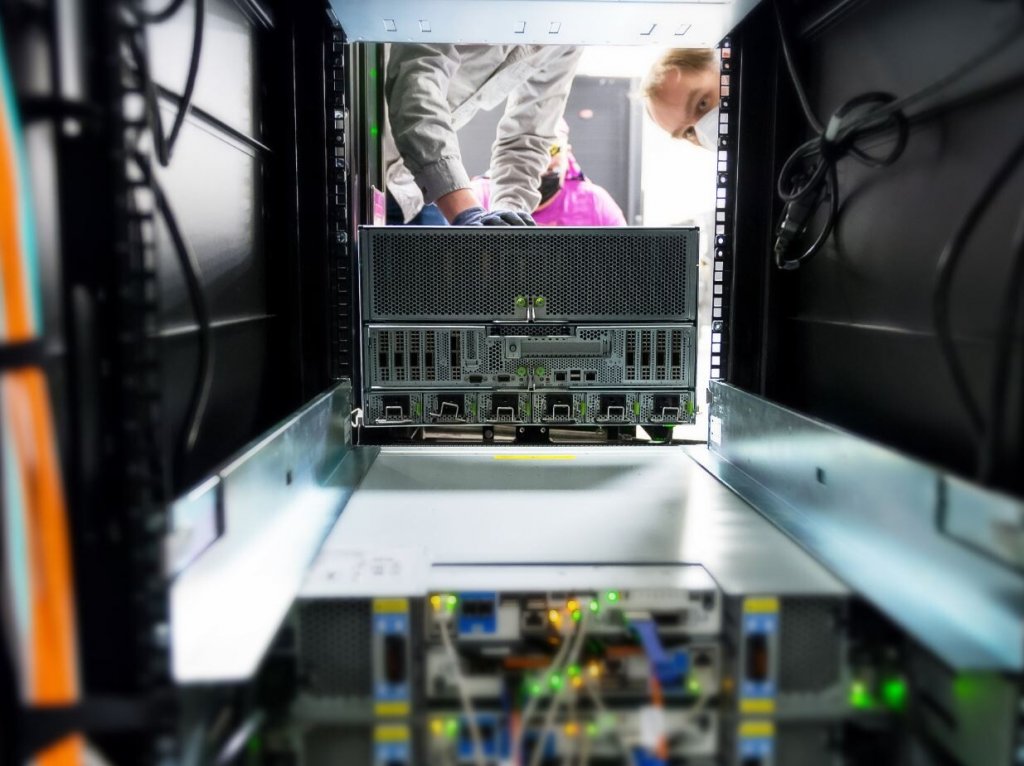

Nową funkcją związaną z HPC wprowadzoną w A100 jest procesor graficzny z wieloma instancjami, który pozwala na uruchamianie wielu złożonych aplikacji na tym samym GPU bez współdzielenia zasobów, takich jak przepustowość pamięci. Użytkownik może teraz podzielić fizyczny A100 na maksymalnie 7 wirtualnych GPU o różnych specyfikacjach i upewnić się, że aplikacja działająca na jednym z vGPU nie zużyje zasobów drugiego. Jeśli chodzi o rzeczywistą wydajność, NVIDIA twierdzi, że A100 pokonało V100 7 razy w BERT. Stacja DGX-A100 składająca się m.in. z 8 układów Tesla A100, będzie kosztować 190000 dolarów.

Źródła: TechPowerUp